曾益慧创杯赛题分析

赛题任务

555定时器芯片的的设计验证和测试(模拟IC设计、验证、测试)

http://univ.ciciec.com/nd.jsp?id=890#_jcp=1 (赛题链接)

题目解读

关键词:555定时器 EDA工具

1、 555定时器

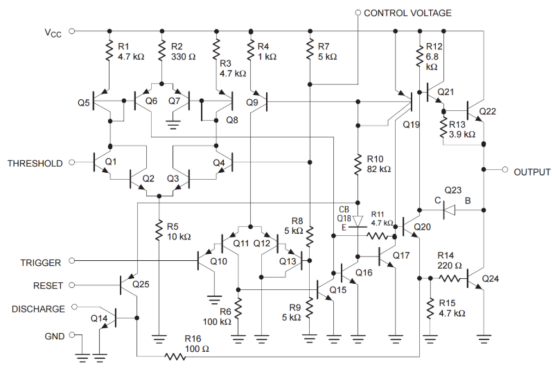

555定时器是一种多用途的,集数字、模拟于一体的8引脚时基集成电路,其应用极为广泛。它不仅用于信号的产生和变换,还常用于控制和检测电路中。由于使用灵活、方便,故而在波形的产生与交换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。可在双稳态模式(施密特触发器)、单稳态模式、无稳态模式(多谐振荡器) 三种模式下工作。内部结构一般由分压电路、比较器电路、锁存器电路、触发器电路等组合而成,具体电路结构根据设计指标和要求而改变。

2、EDA工具

EDA(电子设计自动化)工具 是指利用计算机辅助设计来完成集成电路芯片功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计工具,涵盖了电子设计、仿真、验证、制造全过程的所有技术。不同的 EDA工具 功能侧重点不同,需要根据实际选择。 完成555定时器模拟IC设计需要的EDA(推荐)

- Cadence Virtuoso

adence Virtuoso 是一款专业的集成电路设计工具,提供了从电路设计、仿真到版图设计的全流程解决方案。。对于 555 定时器这类 IC 电路的设计,它可以进行精确的电路级和版图级设计。

- Synopsys HSPICE

HSPICE 是一款业界标准的电路仿真工具,它支持多种仿真模式,能对复杂的模拟电路进行详细的性能分析。在 555 定时器 IC 电路设计中,它可以帮助你准确预测电路的行为和性能。

设计指标(基础)

- 完成555定时器芯片的电路和版图设计工作,包括设计阶段的前仿和后仿验证工作

根据杯赛给出的功能要求、性能指标使用0.18μm工艺进行设计。在保证满足芯片功能指标的同时需要注重设计的完整性,并通过DRC、LVS验证,以设计出能达到要求的的芯片为首要条件,后期再进行优化。需要注意在原理图设计时指标要求留出一定余量,避免版图寄生参数提取后的后仿真不通过。

设计指标(优化)

- 创新性:电路架构和算法是否有创新

- 后仿真结果分析及优化

- 满足技术指标下,面积和功耗越小越好

评分机制

具体材料见官网要求,在此只做分析总结

初赛

需要设计出一个555定时器芯片,关键在于保证原理图、版图设计、前仿真和后仿真的数据完整,电路架构设计以合理且满足性能指标优先,在保证自身能力足够的前提下再考虑复杂的电路结构,避免在后期优化困难。

分区决赛

本杯赛的分区决赛采用现场硬件搭建、测试的形式,简单地说在初赛阶段的设计成果并不会用到分区决赛中,在本阶段需要完成电路板卡上空缺元器件的测试选型,并对整个电路完成现场要求的测试工作,需要更深入且全面了解555定时器芯片的结构和性能。

全国总决赛

本阶段同样采用现场测试、开发的形式进行,完成555定时器芯片量产测试程序开发,实现芯片的自动化测试,需要注意的是测试软件框架基于LabVIEW实现。

LabVIEW是一款图形化编程语言,芯片自动化测试中应用非常广泛,网上有很多开源教程。

参考资料

555定时器原理及应用 555定时器工作原理与常见应用 模拟IC设计全流程 EDA软件工具推荐

学习路线

- 学习模电、数电、电路设计、版图设计,555定时器芯片属于集成块,涉及知识较广,只需要重点学习相关部分,否则时间成本太高。

- 选择一个EDA工具,大部分功能较完善且操作友好的EDA软件(如Cadence, Synopsys, Mentor等)一般都需要在Linux系统下操作,具体选择根据实际进行。

- 完成基础理论学习后,先架构芯片电路整体框架,在电路搭建完成后进行前仿真,根据进行结构和参数调整;在进行版图设计时要重点关注版图布局布线是否合理,同时尽量减小寄生参数,完成后进行DRC和LVS验证,通过后提取寄生参数进行后仿真,根据指标要求不断迭代修改。