叩特杯赛题分析

赛题任务

USB2.0协议的数据链路层模块设计。

http://univ.ciciec.com/nd.jsp?id=884#_jcp=1 (赛题链接)

题目解读

关键词: USB2.0 前后端

USB2.0简介

USB 2.0(Universal Serial Bus 2.0)是一种广泛应用的高速串行总线标准。这里只简单的介绍USB2.0

物理层

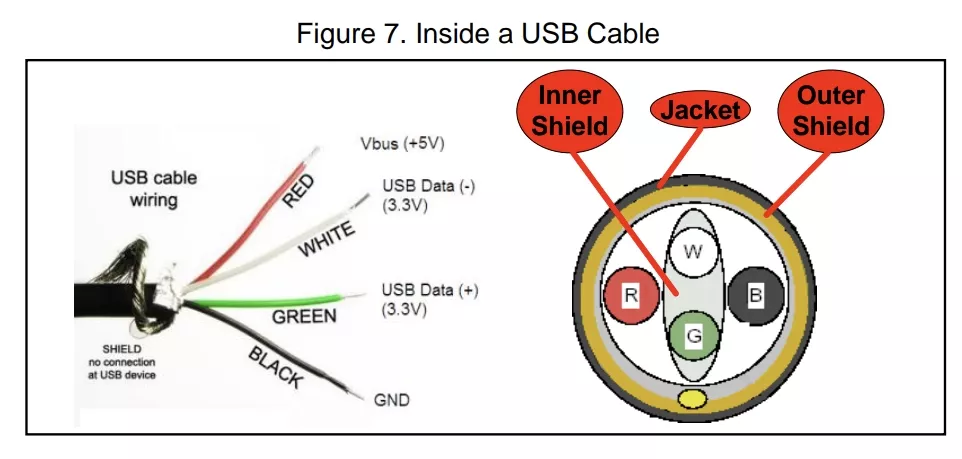

USB 2.0 使用 四根线,分别为:

- VBUS(+5V):供电线,为设备提供电源。

- GND(地线):电源地线。

- D+ 和 D-(数据线):差分信号对,用于数据传输

链路层

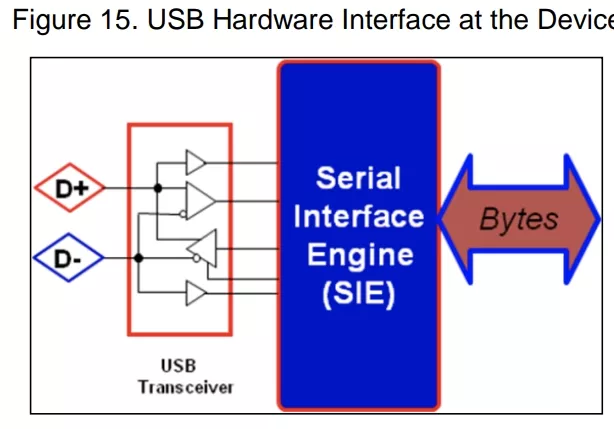

USB 接口需要两个主要硬件模块:收发器(也称为 PHY,物理层的缩写)和串行接口引擎(也称为 SIE)。收发器提供 USB 连接器与控制USB 通信的芯片电路之间的硬件接口。SIE 是 USB 硬件的核心。它执行多种功能,如 USB 数据的解码和编码、纠错、位填充和信令。

物理层接收到了数据,会给到数据链路层去做一些纠错,解码的操作,我们设计的模块就类似于SIE。仔细阅读USB2.0的手册,其中关于通讯协议的部分解释了你具体需要实现的功能,,需要详细阅读。

-

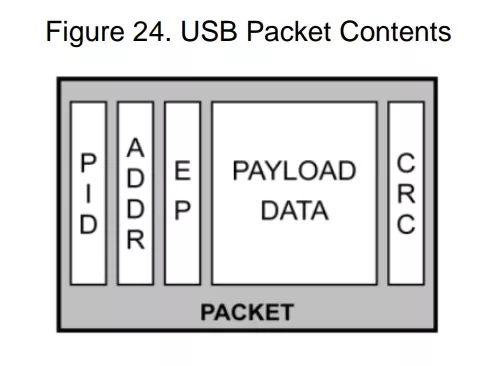

数据包标识(PID) – (8 位:4 位类型位 + 4 位错误校验位)。这些位用于声明事务类型,如 IN/OUT/SETUP/SOF。

-

可选设备地址(ADDR) – (7 位:最多支持 127 个设备)。

-

可选端点地址(EP) – (4 位:最多支持 16 个端点)。USB 规范支持最多 32 个端点。虽然 4 位的端点地址最大值是 16,但通过 IN PID 和端点地址(1 到 16)以及 OUT PID 和端点地址(1 到 16),可实现总共 32 个端点。请注意,这里指的是端点地址,而不是端点编号。

-

可选有效载荷数据(PAYLOAD DATA) – (0 到 1023 字节)。

-

可选 CRC 校验 – (5 位或 16 位)。

前端

工具

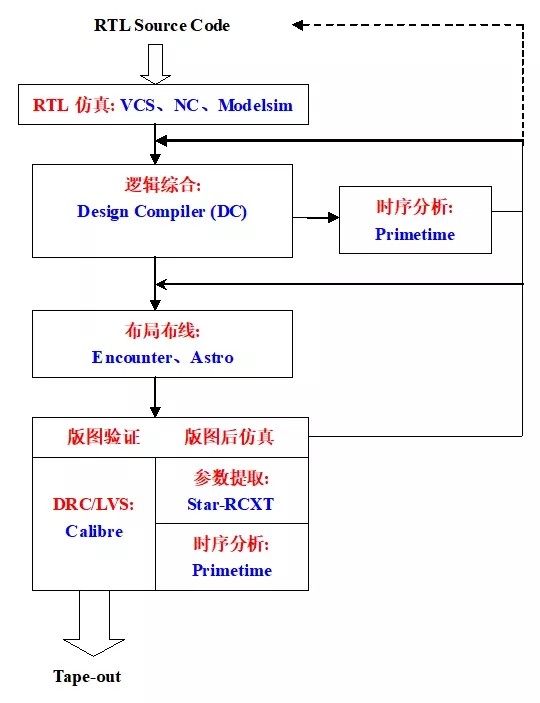

叩特在比赛中会提供服务器和比赛需要用到的后端软件:VCS、Verdi、Design Compiler,Prime Time。

VCS:HDL仿真

Verdi:加载波形文件,查看信号的波形及其对应的代码来进行调试

Design Compiler:生成网表

Prime Time:STA(时序分析)

后端

在设计及仿真自测流程完毕的基础上,后端flow完成基于Innovus的APR环境搭建,完成设计初始化并检查网表、时序等,完成FloorPlan阶段对芯片面积规划以及IO port的摆放,完成时钟树单元及NDR绕线规则的指定、配置CTS相关参数及设置,配置Route相关option及参数并完成最终绕线,完成postRoute阶段的优化工作,完成PR之后的STA相关工作。要求完成后端基本流程实现,并经过多次优化,输出netlist、def和lib等文件。

名词解释

Innovus:软件;后端流程中,Innovus用于完成从网表到最终布局的所有物理设计步骤,包括FloorPlan、Place、Route、Optimization等

APR环境:Automated Physical Design,自动化物理设计。用于自动化完成芯片物理设计的流程,包括布局、绕线、时钟树合成等

FloorPlan阶段:FloorPlan是物理设计的第一步,主要用于规划芯片的面积、形状、模块布局以及I/O端口的位置。

时钟树单元:时钟树单元是用于生成和优化时钟网络的模块

NDR绕线规则:Non-Default Routing(非默认绕线)规则。NDR规则用于定义特殊的绕线需求

CTS:Clock Tree Synthesis(时钟树合成)。用于自动生成和优化时钟树网络的过程

Route:Route是指在物理设计中为网表中各个模块之间的连接分配具体的物理路径的过程

postRoute阶段:postRoute阶段是指绕线完成后,对设计进行的优化和检查,包括时序优化、信号完整性分析等

PR:Physical Design(物理设计)。PR是指将前端设计的网表转化为物理布局的过程,包括FloorPlan、Place、Route等步骤

STA:Static Timing Analysis(静态时序分析)。分析芯片中所有时序路径的延迟,确保设计满足时序要求

netlist:Netlist是描述数字电路中模块之间连接关系的文件,通常由前端设计工具生成

def:DEF文件是用于描述芯片物理布局的标准格式文件,包含模块的位置、绕线信息等。DEF文件是后端设计的输出文件之一,用于记录最终的物理布局结果。

lib:Lib文件包含了标准细胞的功能、时序和功耗信息,是前端设计和后端设计的重要输入文件。Lib文件为后端设计提供了标准细胞的物理和时序模型,用于实现物理设计和时序分析。

工具

叩特在比赛中会提供服务器和比赛需要用到的后端软件:Prime Time、StartRc、Formality、innovus。

Prime Time: 静态时序分析(STA)

StartRc:寄生参数提取

Formality:形式验证工具

Innovus:布局、绕线、时钟树合成和优化

设计指标/评分机制

初赛

仅看RTL代码以及仿真

分赛区决赛

仿真以及输出网表文件

全国总决赛

完成后端流程

开发环境

仿真fsdb文件(波形),TSMC 65nm工艺库相关文件;EDA工具:VCS、Verdi、Design Compiler、Prime Time、StartRc、Formality、innovus

参考资料

USB 101: An Introduction to Universal Serial Bus 2.0

USB 2.0 Specification(你应该只需要阅读其中的usb_20.pdf)

学习路线

-

HDL语言(verilog)与数电

-

USB2.0的手册

-

前端设计的各种工具软件(通过VCS仿真,Prime Time进行STA)

-

后端设计的各种工具软件